在日本科學技術振興機構(JST)的戰略性創造研究推進事業中,東京大學生產技術研究所的小林正治副教授等人成功開發了溝道採用8nm金屬氧化物半導體IGZO(*1)的電晶體型鐵電記憶體(FeFET)。利用該技術,實現了能在亞閾值斜率為理想的60mV/dec、存儲窗口(Memory Window)為0.5V以上的高遷移率下,以低電壓工作的優異存儲特性。

*1 由In-Ga-Zn-O構成的材料,在非晶狀態下為半導體,遷移率為10~100cm2/Vs,目前主要用於顯示器的驅動電路等。

柵極絕緣膜採用鐵電二氧化鉿(HfO2)的FeFET作為低功耗、大容量記憶體件備受關注,不過溝道採用硅的器件結構會形成低介電常數界面層,由於界面層的電壓降低,而且會發生電荷擷取,因此難以同時實現低電壓和高可靠性。

為了抑制界面層的形成和電荷擷取的影響,在三維堆疊結構下也能獲得大的數據擷取電流,該研究提出了溝道採用金屬氧化物半導體IGZO的鐵電HfO2柵極絕緣膜FeFET。採用這種器件結構的話,能抑制IGZO與鐵電HfO2之間形成低介電常數界面層。

此次的成果為實現低功耗、大容量的高速記憶體件開闢了新的可能性,有望大幅提高物聯網(IoT)邊緣器件的能量效率、實現高級IoT網路以及完善基於大數據的社會服務。

相關研究成果已於2019年6月11日在「VLSI Technology Symposium 2019」上發表。

<研究背景與過程>

實現讓所有的「物」和「事」都通過網際網路連接的IoT社會,配備感測器和通信功能的感測節點器件發揮著重要作用,據估算,今後將導入數萬億個以上的感測節點。這些IoT器件的功耗必須要低,而且為了削減作為主要功耗的漏電流(電流洩漏),需要使用能降低記憶體待機電力的低功耗非揮發性記憶體。

柵極絕緣膜採用鐵電體的電晶體型鐵電記憶體(FeFET)具有低功耗和大容量的特點。尤其是開發出了與積體電路製造工藝高度相容、10nm以下的膜厚也顯示出鐵電性的鐵電二氧化鉿(HfO2)材料,受到了廣泛關注。另外,還有望採用像快閃記憶體那樣的三維堆疊結構,不僅是IoT器件,還有可能作為伺服器用超大容量記憶體使用。

不過,以往那些溝道採用硅的FeFET,柵極絕緣膜與硅溝道之間會形成低介電常數界面層,界面層的電壓大幅降低,而且會通過界面層進行電荷擷取,難以同時實現低電壓和高可靠性。另外,採用三維堆疊結構時,溝道需要使用遷移率較低的多晶矽,因此數據擷取電流較小,訪問時間可能會延遲。

<研究内容>

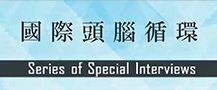

為了抑制界面層的形成和電荷擷取的影響,在三維堆疊結構下也能獲得大的數據擷取電流,本研究提出了溝道採用金屬氧化物半導體IGZO的鐵電HfO2柵極絕緣膜FeFET。採用這種器件結構的話,由於IGZO本身就是金屬氧化膜,能抑制IGZO與鐵電HfO2之間形成低介電常數界面層(圖1)。

圖1

(a)此次提出的三維堆疊型IGZO溝道鐵電HfO2 FeFET的模式圖

(b)採用多晶矽溝道和IGZO溝道的FeFET的特徵比較。採用IGZO溝道能抑制界面層的形成和電荷擷取,可以實現高遷移率。

另外,通過使溝道採用N型摻雜IGZO,可作為無結電晶體工作,載流子通過體區(溝道中央部分)而非界面流動,因此能抑制載流子的電荷擷取。要想讓無結電晶體常閉工作,即在柵極電壓為零時不通電,需要控制閾值電壓,因此將IGZO的膜厚減薄到了10nm以下。膜厚減至10nm以下的話,多晶矽的遷移率低於10cm2/Vs,但IGZO能保持10~100cm2/Vs的高遷移率。

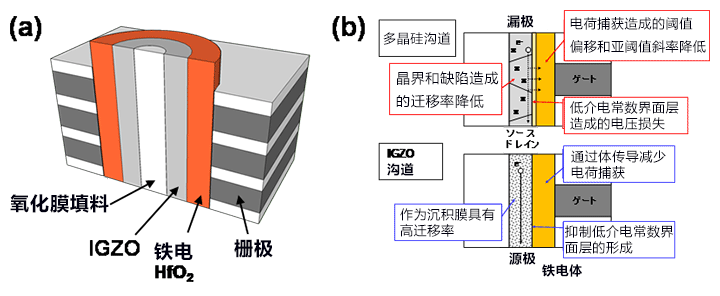

在器件工藝的開發中,首先最適化了IGZO的膜厚。研究小組製作了溝道採用IGZO、柵極絕緣膜採用二氧化矽(SiO2)的普通MOSFET,調查了亞閾值斜率和閾值電壓對膜厚的依賴性,發現隨著膜厚變薄,亞閾值斜率會減小,閾值也由負變為正(圖2)。最終確認,8nm膜厚為最佳值,亞閾值斜率為理想的60mV/dec,閾值電壓也變為正數,能實現常閉工作。

圖2

(a)在開發FeFET的準備階段,採用SiO2作為柵極絕緣膜製作的MOSFET的電流傳輸特性

(b)從(a)的數據中提取了亞閾值斜率和閾值電壓。膜厚越薄,亞閾值斜率越陡,閾值電壓也變為正數。本次研究以8nm為目標膜厚。

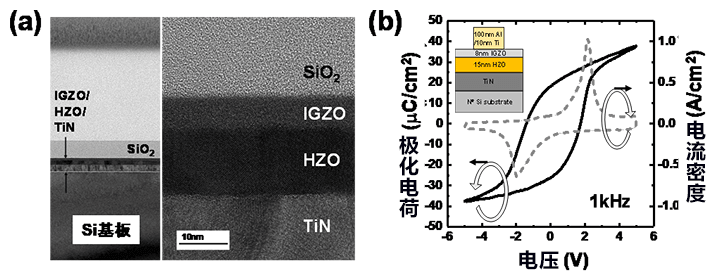

接下來調查了溝道採用IGZO時,柵極絕緣膜HfO2是否具有鐵電性。研究小組以TiN為上部電極、以IGZO為下部電極,製作了添加Zr的HfO2(HfZrO2)電容並進行了評測(圖3)。從截面TEM圖像中可以看出,沒有形成界面層(圖3(a)),另外,表示鐵電體特性的剩餘極化達到30μC/cn2,顯示出非常高的值(圖3(b)),表明能在IGZO溝道上形成鐵電HfO2。

圖3

(a)製作的TiN/HfZrO2/IGZO電容的截面TEM圖像

(b)電容的極化電荷及電流密度特性。確認抑制了低介電常數界面層的形成,能在IGZO上形成鐵電HfO2。

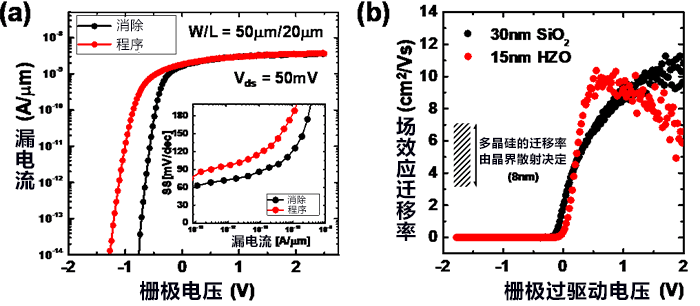

研究小組利用以上工藝要素,製作了溝道採用8nm膜厚IGZO的鐵電HfO2柵極絕緣膜FeFET(圖4)。電流傳輸特性顯示出良好的特性,電流的開關比達到5位數以上(圖4(a)),亞閾值斜率也與MOSFET獲得的結果相同,實現了約60mV/dec的陡峭特性。另外,對場效應遷移率進行測量,獲得了10cm2/Vs以上的值,比相同膜厚的多晶矽溝道高出50%以上(圖4(b))。

圖4

(a)製作的IGZO溝道FeFET的電流傳輸特性

(b)場效應遷移率。亞閾值斜率為60mV/dec,幾乎屬於理想值,實現了具備0.5V以上的大存儲窗口的FeFET。FeFET結構的場效應遷移率也獲得10cm2/Vs以上的值,高於相同膜厚的多晶矽的遷移率。

通過將硅以外的新材料溝道用於記憶體,FeFET實現了低電壓、高可靠性和高遷移率,由此提示了開發記憶體件的新方向,並開闢了進一步實現低功耗化、大容量化和高速化的可能性。

<未來展望>

為了驗證溝道採用IGZO的FeFET概念,本次研究中使用了背柵型器件結構。今後採用頂柵型和三維堆疊型結構時,需要開發和評測堆疊型柵極結構。另外,為了提高保持特性,將調整鐵電HfO2柵極絕緣膜的材料特性,為應用於IoT和存儲類主記憶體,將繼續進行器件開發,計劃實現1.8V的工作電壓並提高改寫速度,還將實現10年的數據保存、1012次的改寫耐性以及1~10mA的擷取電流等。

(日文發布全文)

文:JST客觀日本編輯部