東京工業大學工學院電氣電子系的岡田健一教授等人與日本電信電話術公司組成的研究團隊,成功開發出了採用300GHz頻帶的超高速無線通信收發器,頻率達到5G使用的28GHz頻帶的10倍。

這款無線收發器的發送和接收功能加在一起,隻需410mW的低功耗即可實現34Gbps(Gbit/秒)的高速無線通信。通過採用新設計的高增益混頻器電路,可利用能低成本量產的硅CMOS工藝製造。

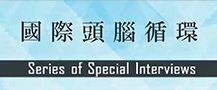

圖1:新開發的300GHz頻帶無線設備IC(安裝在印刷電路板上後)

隨著實現低成本化、小面積化和節電化,可以將其配備於智慧型手機等移動終端。這一成果將加速推進5G的下一代無線通信系統的實用化。

相關論文已在8月4日開始線上舉行的國際會議IMS 2020(International Microwave Symposium 2020)上發表,演講題目為「A 300GHz Wireless Transceiver in 65nm CMOS for IEEE802.15.3d Using Push-Push Subharmonic Mixer「。

開發背景

日本從2020年3月開始提供5G服務,關於5G的下一代無線通信的研究也已經在積極推進。為實現更高速度、更大容量的無線通信,比5G的毫米波頻帶高10倍以上的300GHz頻帶的利用備受期待。

一般來說,5G利用28GHz頻帶的頻率可實現最高10Gbps的通信速度。通過進一步提高頻率,採用300GHz頻帶,有望增加可利用的通信頻寬,實現最高300Gbps以上的無線通信。為盡快實現300GHz頻帶無線設備的實用化,亟需開發小型、低成本,而且將來可以配備於移動終端的節電技術。

課題

此前也發布過採用成本方面佔優勢的硅CMOS工藝的300GHz頻帶無線設備,但存在難以削減耗電能和電路面積的課題。原因是,300GHz頻帶難以在硅CMOS上實現放大器,在這樣的制約下,要想提高無線設備的輸出功率,就要採用多個小輸出功率的電路,然後使輸出功率相加。

因此,無線IC上配備的收發器的數量就會增加,導致耗電能和面積增大。另一方面,採用高頻特性更優異的磷化銦(InP)等化合物半導體,也可以實現300GHz頻帶的放大器,但在整合方面存在課題。

研究成果

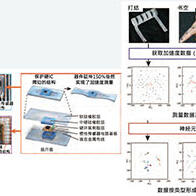

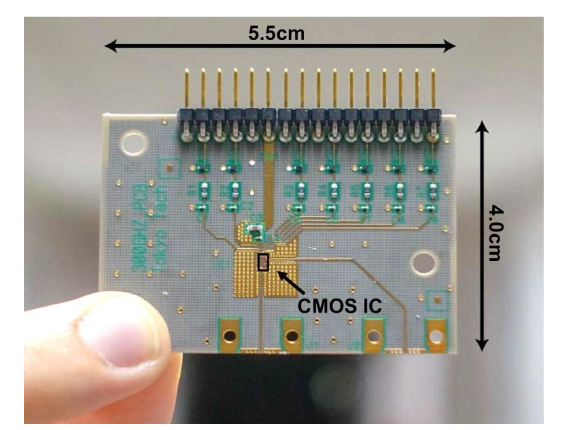

本研究新設計了高增益混頻器電路,從而成功開發出即使採用硅CMOS工藝也能以小面積、低功耗工作的無線收發器。圖2是此次開發的無線收發器的整體構造。發送器和接收器都採用新開發的混頻器電路,因此無需在天線和混頻器之間安裝放大器,即可實現無線通信所需的高信號雜音比(SNR=Signal-Noise Ratio)。

圖2:新開發的300GHz頻帶無線收發器的構造

在以往的混頻器中,中間頻帶的調變信號和用於變頻的本地信號都從同一個端子輸入,因此利用電晶體的電壓電流轉換的非線性進行變頻,難以提高混頻器電路的增益(電路的輸入輸出比)。另外,還要使兩種信號的阻抗匹配,因此需要使中間頻率和本地信號頻率在同一頻帶内,而且調變波信號和本地信號都需要使用超過100GHz的放大器。

放大器的耗電能會隨著頻率增加,這是以往的無線收發器耗電能較大的原因之一。此次新設計了可以使調變信號和本地信號從不同端子輸入的混頻器電路結構。通過採用這種結構,可以利用電晶體的開關進行變頻,成功地將混頻器電路的增益較原來提高了約2倍。另外,利用這種方式還可以將中間頻率設定為100GHz以下,因此能大幅削減耗電能。

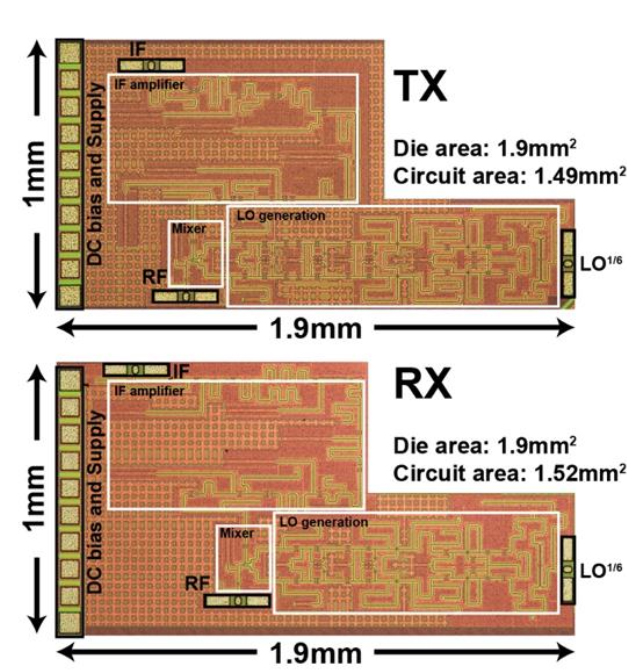

研究團隊利用硅CMOS 65nm工藝試製了新開發的300GHz頻帶無線收發器(圖3),通過對300GHz頻帶的無線通信特性進行測量評估,確認了所提出的技術的有效性。收發器可在278GHz至304GHz的頻率下滿足IEEE802.15.3d無線標準規定的頻率圖譜模板(Spectrum Mask),能應對從QPSK到16QAM的調變方式。

圖3:試製的無線收發IC的照片

最大通信速度為34Gbps,此時,發送器和接收器的耗電能共410mW,與此前研究中採用硅CMOS工藝的300GHz頻帶收發器相比,耗電能降至四分之一以下。另外,無需使用多個收發器進行功率合成,隻使用一個收發器即可構成,因此收發器整體的晶片面積只有3.8mm2,節省了面積。

未來展望

此次開發的300GHz頻帶無線收發器採用硅CMOS工藝,節約了耗電能和面積。從而可以削減無線設備的尺寸,配備於移動終端,通過CMOS工藝節約了面積的無線IC還有助於降低無線設備的成本。今後將以此次的研究成果為基礎繼續推進開發,計劃進一步提高速度,使新一代100Gbps以上的超高速、大容量300GHz頻帶無線通信實現實用化。

文:JST客觀日本編輯部