把半導體製造技術留在日本——日本的國家項目「先端半導體製造技術開發」帶著這個悲壯感的目標於2021年度啟動。半導體代工巨頭臺灣積體電路製造(TSMC)的參與也引發了關注。

位於茨城縣筑波市的「產業技術綜合研究所」的設施將作為項目基地(供圖:產綜研)

該項目是新能源產業技術綜合開發機構(NEDO)2019年度開始推進的項目的一部分。以擁有最先進清潔車間的產業技術綜合研究所(茨城縣筑波市)為基礎,企業和大學將在這裏開發具有支撐數字社會發展的運算功能的邏輯半導體製造技術。

| 項目概要 | |

| 名稱 | 先端半導體製造技術開發 |

| 内容 | 開發“後5G”時代的尖端邏輯半導體製造技術,確保可以在國内製造 |

| 開始 | 2021年度 |

| 預算 | 760億日元(5年的預估補助額) |

| 參與機構 | 產業技術綜合研究所、東電電子、佳能、TSMC日本3DIC研究開發中心、先端系統技術研究組合等 |

半導體製造工序分為利用曝光設備等在硅基底層上形成電路的「前工序」和將其切割並組裝的「後工序」。本次的項目也以這兩道工序為研發主題,共同的關鍵字是「三維」。

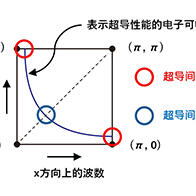

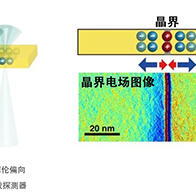

前工序致力於將名為「奈米片」的細結構上下排列的最尖端器件技術。目前邏輯半導體的基本結構已經由在基底層表面形成的二維「平面型」變成了路塹基底層製作有一定厚度的「鰭型」,其被稱為「2.5維」。預計2025年以後三維奈米片型將成為主流。

日本擁有量產技術的是平面型,該項目將跳過鰭型,直接致力於三維奈米片型。東電電子、迪恩士(SCREEN Semiconductor Solutions)和佳能將在產綜研的設施裏建設試產線。

後工序將確立縱向堆疊的積層電路技術。主角為TSMC的日本研究基地TSMC日本3DIC研發中心。計劃與日本方面共同開發名為「3DIC」的三維後工序技術。作為其他開發項目,產學共同參與的「先端系統技術研究組合(RaaS)」將致力於晶片的三維積層技術。

三維整合是打破半導體微細化「摩爾定律」極限的有力技術。尤其是後工序相關的技術,日本企業被認為擁有優勢,受此吸引的TSMC與希望聯合該公司的日方想法剛好一致。

文:吉川和輝 編輯委員、《日本經濟新聞》,2022/04/04

翻譯編輯:JST客觀日本編輯部