東京大學生產技術研究所的小林正治副教授與奈良先端科學技術大學院大學的浦岡行治教授等人組成的聯合研究團隊,開發出了利用原子層沉積物(ALD)法取代常規濺射法成膜氧化物半導體氧化銦(In2O3)的技術,並成功開發出了三維垂直溝道型鐵電和反鐵電的電晶體記憶體。

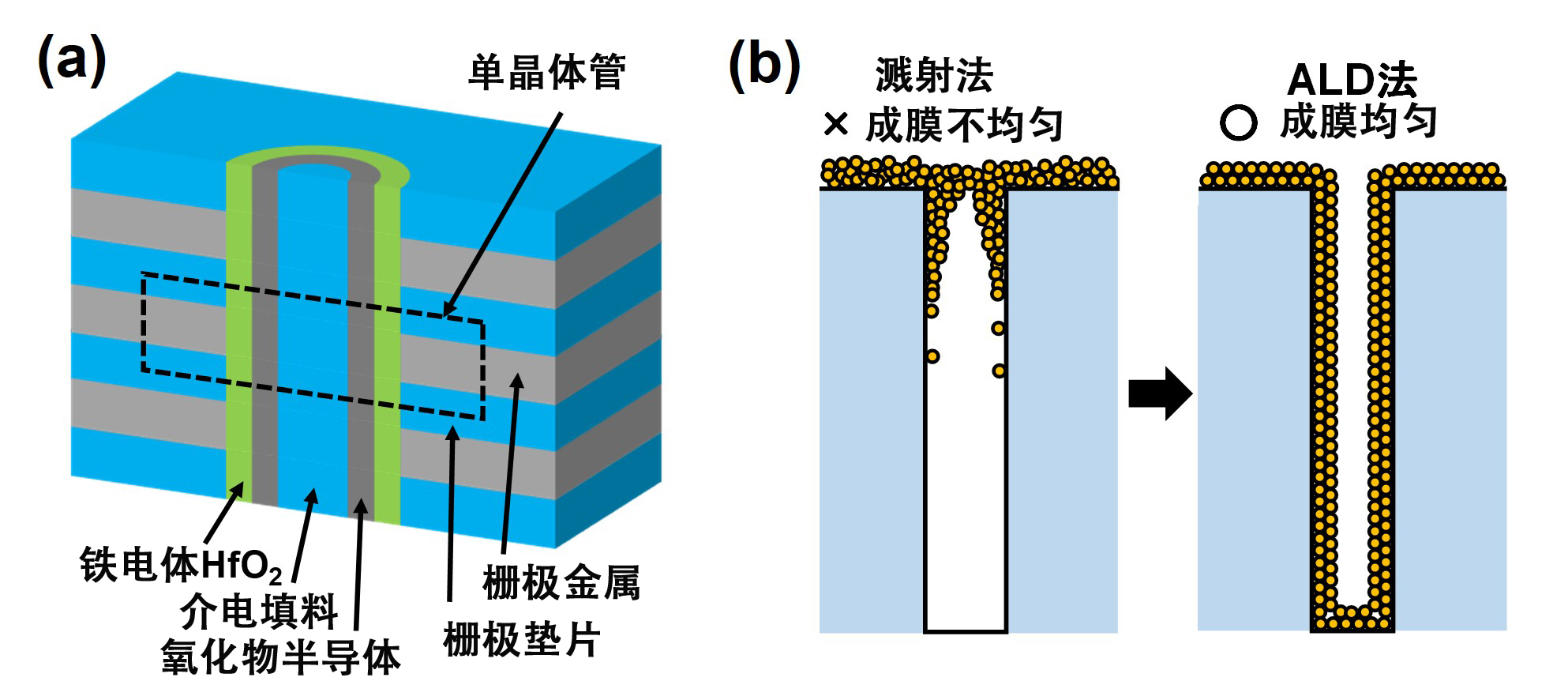

圖1:(a)此次提出的使用氧化物半導體作為溝道的三維垂直溝道型FeFET的模式圖。柵極絕緣膜使用鐵電材料HfO2。(b)氧化物半導體三維成膜時存在的問題和解決方法。通過使用ALD法,可以均勻形成三維結構薄膜。(供圖:東京大學生產技術研究所副教授 小林正治教授)

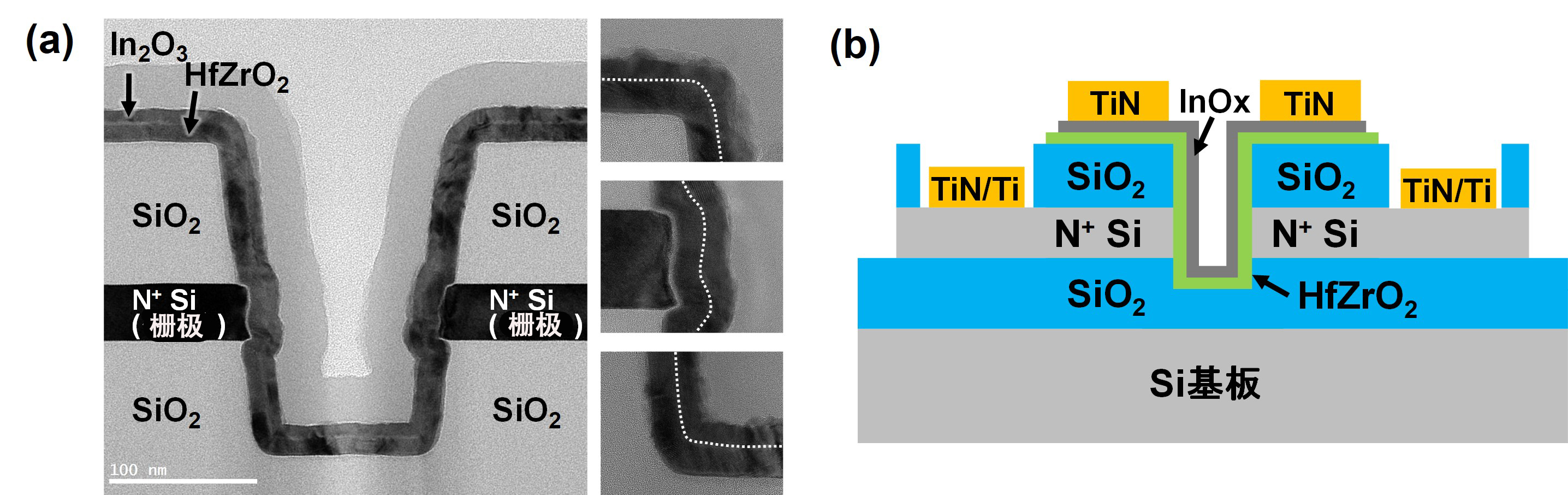

圖2:(a)試製的三維垂直溝道型FeFET的截面穿透電子顯微術(TEM)照片。鐵電材料HfO2和氧化物半導體In2O3都均勻成膜。(b)試製的原型器件整體的截面模式圖。(供圖:東京大學生產技術研究所副教授 小林正治教授)

隨著大數據越來越多地得到應用,不僅是雲伺服器,IoT邊緣器件也需要大容量低功耗的記憶體。因此,研究團隊著眼於鐵電晶體管(FeFET)記憶體,通過用原子層沉積物法成膜以前大多通過濺射法成膜的氧化物半導體,開發出了三維垂直溝道型FeFET。另外,還開發了可以更有效地進行重寫的反鐵電晶體管(AFeFET)記憶體。

利用通過ALD法成膜的In2O3製作的薄膜電晶體顯示出每平方釐米超過40Vs的高遷移率。另外,研究團隊還利用ALD法將In2O3均勻形成了三維結構薄膜。並且利用該成膜技術,試製了也可以同樣用ALD法成膜的二氧化鉿鋯(HfZrO2)鐵電材料為柵極絕緣膜的FeFET,驗證結果顯示,如理論預測一樣,具有1.5V左右的存儲窗口(閾值電壓差)、10的4次方以上的重寫耐性和10的3次方秒以上的保持特性。

此外,研究團隊還提出了一種使用反鐵電ZrO 2作為柵極絕緣膜的反鐵電晶體管(AFeFET)。氧化物半導體為N型半導體,雖然容易誘導作為多數載子的電子,但不容易誘導作為少數載子的電洞,因此特點是,相對於程序狀態來說,擦除狀態的保持特性容易劣化。通過使用反鐵電材料,即使不誘導少數載子,也能有效執行擦除操作,可以改善擦除狀態的保持特性。研究團隊經過驗證確認,實際具有0.7V左右的存儲窗口、10的4次方以上的重寫耐性和10的3次方秒以上的保持特性。

小林副教授表示:「這種記憶體件技術密度高、功耗低,因此通過應用於IoT器件的記憶體,有望開展使用大數據的社會服務。為實現更高的整合度和可靠性,今後將推進器件設計及材料和工藝開發,目標是為IoT邊緣器件配備大容量記憶體。」

【詞注】

■原子層沉積物(ALD)法:傳統的化學氣相沉積法之一。在短時間内將反應前驅體以脈衝方式送入反應室,並使其在成膜晶圓上進行單分子層飽和,然後以脈衝方式在短時間内供應作為氧化劑的水和氧等,使飽和的分子層氧化,形成原子層氧化物。通過重複這個過程可以在每個原子層上成膜。特點是,不僅是平面成膜,三維結構也可以實現負載效應較小的均勻成膜。

原文:《科學新聞》

翻譯編輯:JST客觀日本編輯部

【論文資訊】

期刊:2022 IEEE Silicon Nanoelectronics Workshop

論文:A Vertical Channel Ferroelectric/Anti-Ferroelectric FET with ALD InOx and Field-Induced Polar-Axis Alignment for 3D High-Density Memory

URL:snw2022.conf.nycu.edu.tw/