日本東京工業大學和青井電子株式會社(AOI Electronics)等組成的研究團隊把多個功能不同的多個半導體晶片連接起來,使其像單個晶片一樣工作。這樣容易提高晶片的整合密度和電氣特性,改善成品率。在目前半導體微細化工藝接近心極限的情況下,該技術作為替代微細化工藝來提高半導體性能的一種方法而被受期待。

利用新開發的小晶片整合技術試製的樣品

多年來,半導體一直按照約兩年性能翻一番的「摩爾定律」演化。其原動力是減小構成半導體晶片的電晶體尺寸、提高整合度的微細化過程技術。

但半導體的細微化工藝正在迎來其極限。美國蘋果公司9月發售的智慧型手機「iPhone」的最新機型採用了線寬為4nm(1nm為10-9m)的半導體晶片。考慮到物理可用能上的極限,全球能製造這種最尖端半導體晶片的企業僅有臺積電、三星電子等少數幾家。

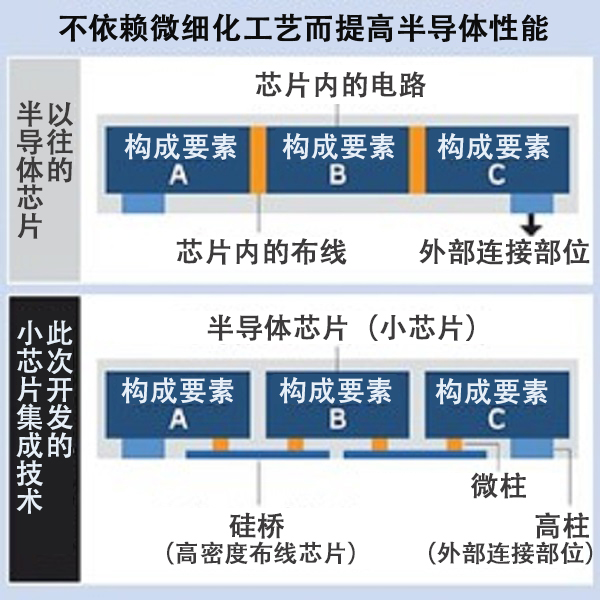

在此背景下,作為新的重點技術而備受矚目的就是基於「小晶片」(chiplet)的整合技術。這種技術做法不是將所有的半導體電路都整合在一個晶片上,而是將各功能要素單獨製造成小晶片,然後像積木那樣相互組合——以電信號方式連接多個小晶片,使其像一個大型晶片一樣工作。

利用這種方法,可以用最先進的工藝製造影像處理等要求高運算能力的電路,用上一代工藝製作輸入輸出電路等。與依賴工藝微細化的現有方法相比,在成品率和成本上更具優勢。

研究團隊此次開發的是,能夠以比之前更簡單地配置與連接小晶片的技術。連接小晶片之間的硅橋(高密度布線晶片)和多個小晶片利用模塑樹脂(mold resin)封裝。小晶片和硅橋通過被稱為「微柱」的微小金屬柱實現電連接。然後使用較大的金屬柱(高柱)貫穿模塑樹脂,將小晶片的集合體與外部連接。

以往,為了連接晶片彼此,多使用名為「插入層」(interposer)的中間基底層。插入層大多用硅來製造,但在氣特性、對位精度、成本等方面都還存在課題。

此次新技術的優點是能夠以最小限度的要素實現小晶片之間以及小晶片與外部之間的連接。小晶片的整合密度容易提高,容易改善電特性,連接部的對位也變得容易。還具有能提高小晶片與外部電連接布線的高頻特性以及熱放射性能的優點。

今後將致力於提高小晶片的整合規模、驗證可靠性等實用化方面的課題。主導這項研究的東工大特任教授慄田洋一郎表示:「首先在日本確立技術,然後向海外拓展。」

為了具體實現上述設想,以東工大、大阪大學、東北大學為中心,有30家左右企業參加的「小晶片整合平台聯盟」於2022年10月成立。除了從事半導體和電子零件業務的青井電子之外,還有住友電氣工業公司等企業。為開發小晶片整合技術,日本的產學研力量開始集結。

就全球範圍來看,2022年3月有10家企業圍繞小晶片技術開展了合作,除了英特爾、臺積電、高通等半導體企業外,還有谷歌、微軟等IT巨頭。這些公司成立了標準化和生態聯盟,公開了晶片連接方式的開放標準「UCIe」。該領域在全球範圍内競爭也很激烈,慄田特任教授指出「日本在半導體材料和製造裝置方面實力很強,都能在小晶片技術中發揮作用。小晶片的普及對日本半導體行業來說是一個機會。」

日文:松元則雄、《日經產業新聞》、2022/11/2

翻譯:JST客觀日本編輯部