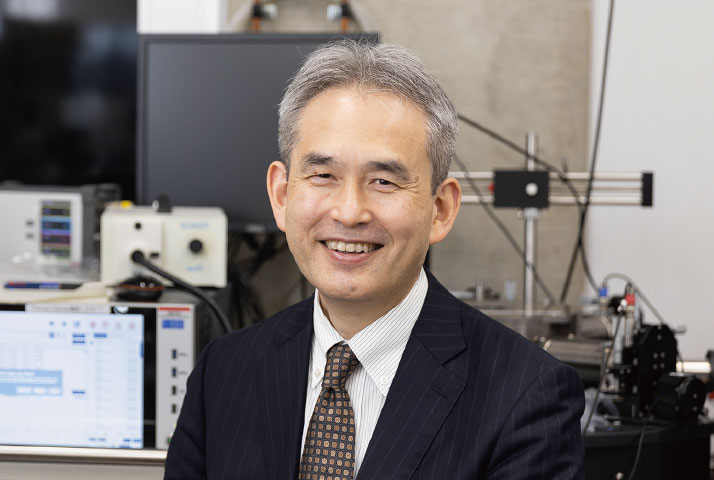

木本 恆暢

京都大學研究生院工學研究科 教授

2018年起擔任OPERA「超智慧能源社會基礎技術共創聯盟」主管

【導讀】為了實現碳中和,使用碳化硅(SiC)功率半導體來節約能源或高效利用能源的技術正在推進之中。京都大學研究生院工學研究科的木本恆暢教授通過大幅降低SiC功率半導體多年來一直存在的氧化膜/SiC界面缺陷問題,確立了同時實現低成本、高可靠性、大幅提高性能的基礎技術。木本教授還在使用SiC半導體的積體電路中驗證了高溫條件下的基本動作,為在多種環境下應用SiC半導體元件開闢了道路。

產學聯盟共享目標

融合學術研究與先進技術

2016年1月,日本政府公佈了「Society 5.0(社會5.0)」概念,明確了日本期待實現的未來社會目標。這是繼狩獵社會(Society 1.0)、農業社會(Society 2.0)、工業社會(Society 3.0)、資訊社會(Society 4.0)之後的以人為本的新社會形態。屆時將由IoT(物聯網,萬物互聯)連接所有人和事物,共享各種知識和資訊,創造前所未有的新價值,以實現經濟發展和解決社會問題。

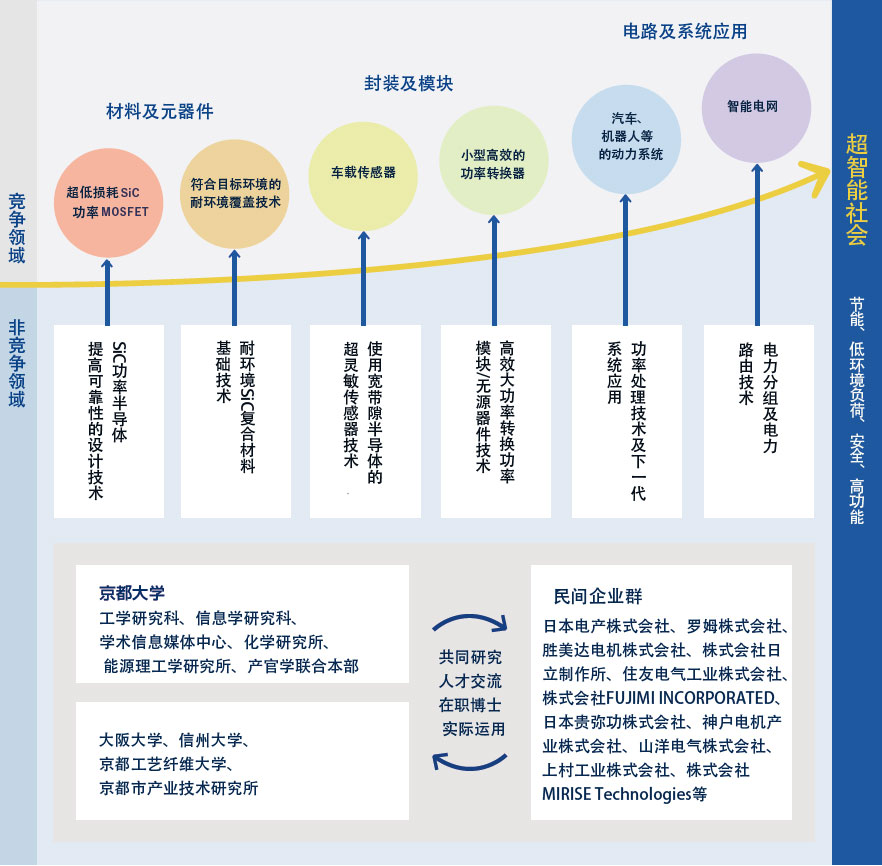

京都大學為了實現「Society 5.0」以及即將到來的極限節能、低環境負荷、安全且高機能社會,於2019年1月成立了開發革新性半導體技術的OPERA「超智慧能源社會基礎技術共創聯盟」(圖1)。該聯盟的主管為京都大學研究生院工學研究科的木本恆暢教授。聯盟的宗旨是在推進創新創發關鍵的學術研究以及和具有普世感的先進技術融合的同時,培養下一代研究者。

圖1 「超智慧能源社會基礎技術共創聯盟」的概要

為了在半導體領域發揮出高水平的國際競爭力,重要的是在發揮技術優勢的同時,開展不僅僅是元器件,還包括周邊設備的研發工作。木本教授介紹說:「聯盟採取的機制是,初期在非競爭領域各加盟單位進行合作研發,當商業化前景確立後,各加盟單位在競爭領域進行個別的聯合研究。」

此外,聯盟還與策劃並實施大規模聯合研究的京都大學開放創新機構、京都府和京都市等地方政府合作,由聯盟的研究人員為從事節能和高效能源利用技術開發的當地企業提供技術指導等,通過與地方合作實現智慧能源的創新。

關於解決問題的關鍵——技術主題,聯盟著眼於激發創新關鍵的學術研究和具有普世感的先進技術的融合,設定了6個主題,分別為「提高SiC功率半導體可靠性的設計技術」、「耐環境SiC複材基礎技術」、「使用寬頻隙半導體的超靈敏感測器技術」、「高效大功率轉換功率模組及無源器件技術」、「功率處理技術及下一代系統應用」、「電力分組及電力路由技術」。

其中木本教授主導的「提高SiC功率半導體可靠性的設計技術」先後誕生了兩項以創新半導體技術為基礎的能源創新成果——分別為解決了長期課題的「通過形成非氧化性氧化膜實現SiC功率半導體(電晶體)的高性能化」,以及「低功耗積體電路在350℃環境下的基本動作驗證」。

Si逐漸達到理論極限

SiC的擊穿場強是Si的10倍

解決能源問題是本世紀最重要的課題之一,但就像可再生能源的充分利用一樣,建立高效利用能源的技術變得重要,而掌握其中關鍵的就是半導體功率器件。從家用電器到光伏發電、電動汽車等,所有帶有電源的電子設備都要用到功率器件,它是支撐人們日常生活的常用器件。

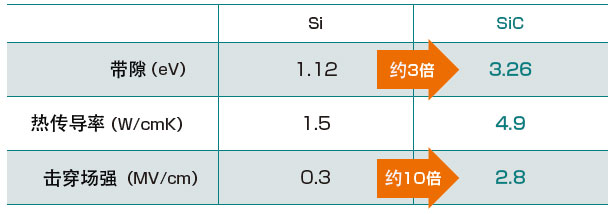

目前的半導體功率器件主要使用硅(Si)材料,但木本教授指出,硅製器件的性能正在接近理論極限,「在不久的將來,將不可避免地需要使用新的半導體材料。其中最有希望的是硅和碳(C)的化合物碳化硅(SiC)」。碳化硅的擊穿場強(表示物質強度的指標之一)是硅的10倍,左右動作上限溫度的帶隙為硅的3倍,而且150mm的大口徑、高品質SiC晶圓已在市場上廣泛銷售,也能夠在大範圍内控制器件所需的p型、n型,所以SiC有望成為超越硅極限的功率器件用材料(圖2)。

圖2 硅與碳化硅的特性比較

雖然日本國内外的企業從1998年就開始正式研發SiC功率半導體,2001年開始量產使用SiC的二極體,但到2010年才開始量產SiC電晶體。以用於工作站等的電源為開端,空調、光伏發電用電力調節器、快速充電器、工業用馬達等設備都開始配備SiC功率半導體。搭載SiC功率半導體的鐵道車輛和電動汽車等也成為了熱門話題。

無需氧化就可製作氧化膜

逆向思維成功降低缺陷

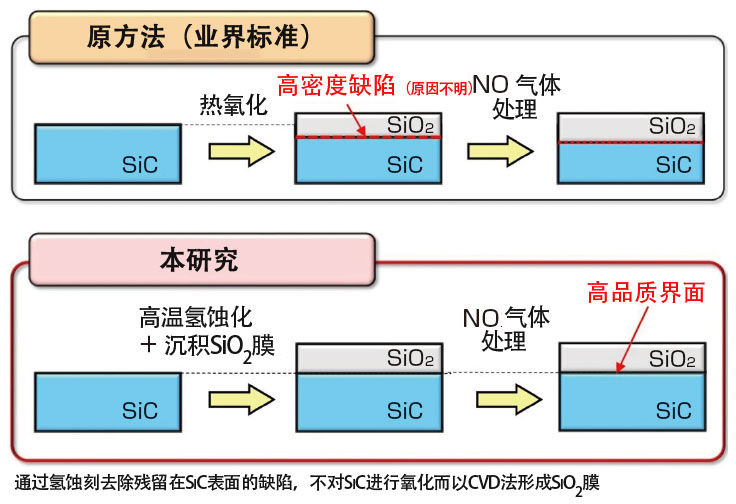

硅功率半導體中最基本且重要的電晶體器件是金屬氧化物半導體場效電晶體(MOSFET)。MOSFET的核心是對硅的表面熱氧化形成的氧化膜(SiO2)與硅之間的界面。碳化硅MOSFET也同樣經過熱氧化,在表面形成SiO2氧化膜,但此時氧化膜與SiC之間的界面會出現比Si大100倍以上的缺陷,這一問題極大地限制了器件的性能。

為了減少這一缺陷,20多年來眾多研究人員不斷嘗試也不斷失敗,幾乎未能取得進展。但是,木本教授等人通過「無需氧化製作氧化膜」的逆向思維,成功地大幅降低了缺陷。東京工業大學物質與資訊卓越教育院的松下雄一郎副教授等人按照第一原理計算發現,SiC熱氧化後,界面必定會高密度出現源於碳原子的缺陷。

根據松下副教授的計算結果,通過基於理論的思考和反復實驗,木本教授等人發現一些工序對減少缺陷是有效的。其中一個是在形成氧化膜之前通過氫侵蝕刻去除殘留在SiC晶圓表面的缺陷,然後在基材表面使用化學成膜的CVD方法來沉積物SiO2的做法。也就是說如果能夠在SiC表面形成高質量的氧化膜,那麼在形成氧化膜時就不會出現新的高密度缺陷。

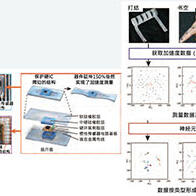

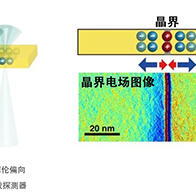

研究團隊在沉積物氧化膜後進一步使用一氧化氮(NO)氣體進行了界面氮化,以實現界面的高質量化(圖3)。結果與原來的業視線誘導標準相比,成功地獲得了將缺陷降低到約1/5的高品質材料,表示載流子易移動性的溝道遷移率也提高了約2倍。

圖3 新提出的SiO2/SiC製作方法

採用微細的溝槽結構

溝道遷移率提高6~80倍

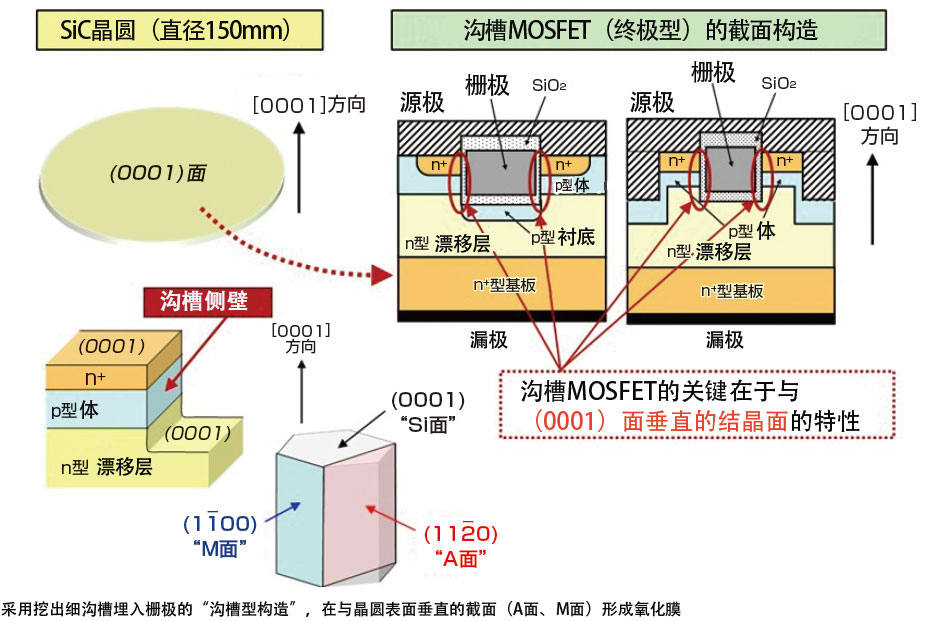

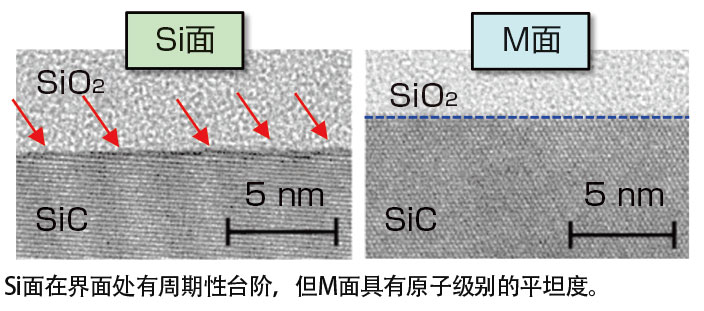

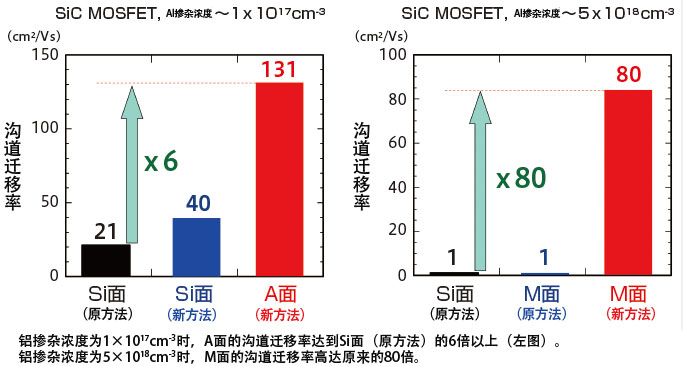

木本教授的研究團隊隨後又進一步設法提高了性能。將晶片的結構由原來在晶圓表面製作柵極的「平面型」改為在表面挖出小溝槽埋入柵極的「溝槽型」,在晶圓表面(0001)面表示的Si面垂直的A面和M面上形成氧化膜(圖4、5)。由此,與以往的氧化膜成膜方法相比,溝道遷移率提高了約6~7倍。

圖4 溝槽型MOSFET截面圖

圖5 SiC製MOS界面電子顯微鏡圖像

此外,與實際製造的SiC電晶體一樣,通過以較高濃度添加受主雜質鋁的方法形成p型區域,並在A面和M面上製造出了MOSFET。由此將溝道遷移率提高到了原方法的6~80倍(圖 6)。這樣一來可靠性大大提高,同時晶片面積減少,使成本可降低到原來的三分之一左右。

圖6 溝道遷移率的比較

木本教授表示,在他30年的研究生涯中,一直苦惱於氧化膜和SiC界面的缺陷。他笑著說:「到目前為止,我先後提出過100多個假設,但都失敗了。一直都是摸著石頭過河的狀態。此次,我們第一次看到了問題的本質,我認為已經找到了根本性的解決方案。」現在,SiC功率半導體的世界市場規模約為1200億日元。預計5年後將增加到3000~6000億日元,如果以此為契機加速SiC功率半導體的實用化,將會為社會的節能做出巨大貢獻。

成功在350℃下確認基本動作

功耗降至萬分之一進入視野

近年來,積體電路的適應範圍擴展到人無法觸及的高溫環境的勢頭越來越盛。在石油和天然氣等的鑽探作業中,地下溫度超過300℃時,就要即時傳遞地下資訊。在行星探測中,金星表面的壓力約為70個大氣壓力,溫度高達400℃以上,偵檢器的著陸變得困難。此外,飛機和汽車的發動機燃燒室内有時會達到600℃,但也還需要在這種環境下精細地控制燃料混合比。

目前主流的硅半導體在250℃左右就會發生故障,所以從理論上不可能應用於這些高溫環境。而碳化硅由於具有在約800℃的環境下也能正常工作的耐熱性所以受到關注。木本教授列舉了此前存在的課題:「SiC MOSFET的核心部分——氧化膜的耐高溫極限約在 250~300℃,且容易受到輻射的影響,因此被認為難以在極端環境下穩定工作。」

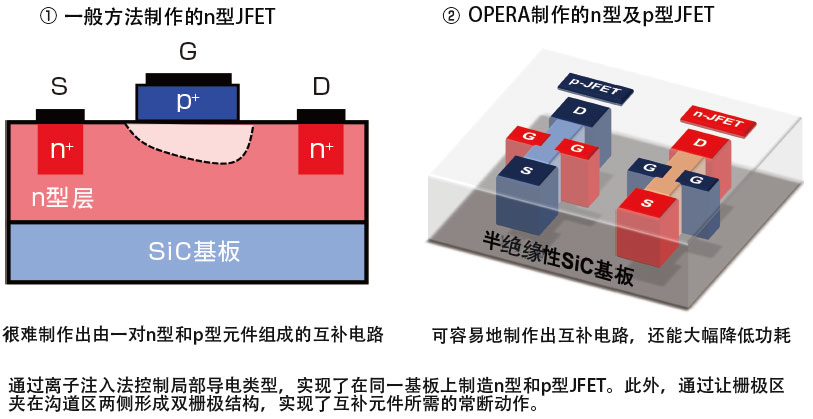

由此受到矚目的是使用 pn 結的結型場效電晶體 (SiC JFET)。由於該器件在構造上本身不存在氧化膜,所以有望作為用於高溫工作SiC積體電路的電晶體。但是,一般方法製作的JFET無法形成互補電路,所以需要大量的待機電力。在SiC積體電路被期待的應用環境——300℃以上的高溫環境下,供電也會受到限制,所以降低功耗一直是SiC JFET面臨的一大課題。

一般的JFET的製作方法只能製成n型或p型中的一種,但木本教授與同一研究室的金子光顯助教等人一起採用離子佈植法,通過用高電壓加速離子化的原子並使其與半導體碰撞並進入半導體内部,從而製作出器件,由此成功地在同一基底層上製作出了n型和p型的JFET。離子佈植法是工業上廣泛應用的技術,從量產的觀點來看也是很有前途的製作方法。

在製造實用型積體電路時,需要配置互補電路以降低待機功耗。為此,當沒有電壓施加到柵極時就沒有電流流過電晶體的常斷特性必不可少。雖然用傳統的製造方法難以實現,研究團隊用兩個柵極從兩側夾住 JFET溝道區域的結構,實現了常斷特性並降低了待機功耗(圖 7)。木本教授自豪地表示:「正如預期的那樣,這樣製作出來的互補型JFET從室溫到350℃的溫度範圍内都能正常工作,並且待機狀態下的功耗也被降至最大只有幾十納瓦甚至更低的程度。」

圖7 JFET的示意圖

與國外開發的使用了JFET的電路相比,木本教授的研究團隊開發的電路功耗不到前者的萬分之一,毫無疑問這是邁向實際應用的一大步。尤其值得注意的是,此次開發的電路可以使用SiC半導體的標準工藝製造,SiC半導體正在與積體電路不同的領域形成市場。木本教授展望道:「JFET是否可以通過微細化來實現小型化、高速化和高功能化,還需要進一步進行基礎研究,我們將繼續進行探討。」 (TEXT:片柳和之、PHOTO:石原秀樹)

原文:JSTnews 2022年12月號

翻譯:JST客觀日本編輯部