日本KDDI綜合研究所和早稻田大學為實現AI運行的低功耗和高速化,成功試製出了面積為傳統產品約1/17的用於光量子AI加速器的硅光量子電路,並成功預測出了時序數據。為了使光量子AI加速器應用於各種場景,雙方將繼續探索和擴展光量子電路的構造及規模,確立相比於GPU基礎的AI加速器,功耗低至1/10,更加高速的光量子AI晶片基礎技術。相關論文被在美國聖何塞召開的光電子學綜合國際學術會議CLEO 2023(The Conference on Lasers and Electro-Optics)所接收,並於5月8日在大會上發表。

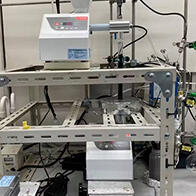

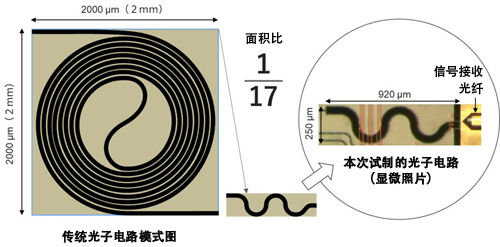

新舊光量子電路對比(供圖:KDDI綜合研究所)

運行最先進的AI需要龐大數量的計算機,所以降低耗電和提高處理速度是目前面臨的課題。通常使用的AI在電子電路上運行。

對此,以光量子電路代替一部分計算的光量子AI加速器在降低功耗方面效果顯著,並且可以提升學習和推論的速度,有望解決AI所面臨的課題,因此相關研發十分火熱。

其中,在硅上形成的光量子電路不僅容易與電子電路及其他光學元件整合化,還有望實現小型化。然而,光量子加速器要想投入實際應用,還需要使其易於大型積體電路,因此需要進一步小型化。

此次雙方研發的面積為傳統產品1/17的光量子AI加速器用硅光量子電路,是在硅上試製的面積為0.25毫米×0.92毫米的光量子電路。為了比較其性能,用其預測作為標準任務的Santa Fe波形,結果發現,正確數據和預測數據的誤差非常小,證明了其結構的有效性。

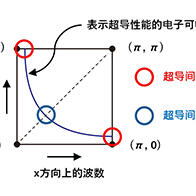

此前的研究的在硅上形成的光量子電路中,為了運行AI模型之一的儲備池計算(Reservoir Computing),需要將現在的資訊和過去的資訊混合,採用以下任意一種結構。

第一種是利用信號形成的網路狀的光量子電路,將現在和過去的資訊多次混合的結構。為了實現有效的混合時機,需要確保網路節點之間的距離,從而導致元件面積增加(16平方毫米)。如果要增加神經元的數量(神經細胞數),則需要更大的面積。

第二種是長螺旋狀多模光波導結構。利用多模光波導可大量存在,並以不同速度傳播的光波的特性,為了混合現在和過去的資訊,需要較長(約4釐米)的光波導。即使將其容納在螺旋狀結構中,也需要大約2mm×2mm的面積。

研究團隊在設計時,與上述第二種結構相比,將波導寬度擴大2倍,且通過用蛇形波導結構調整長度,在產生多個以較短波導長緩慢傳播的光波(高次模式)的同時,通過加速信號,使現在和過去的資訊能夠充分混合。

原文:《科學新聞》

翻譯:JST客觀日本編輯部