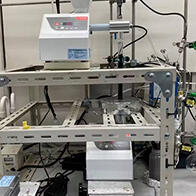

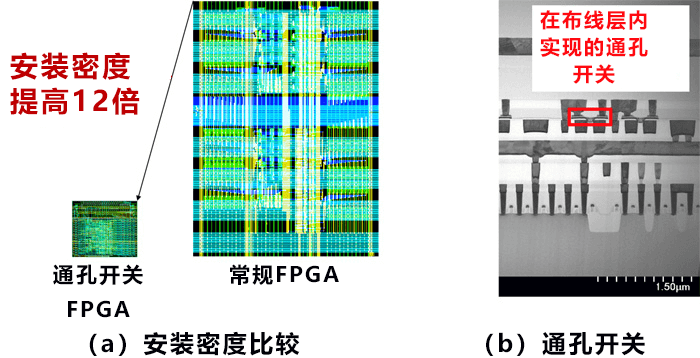

日本大阪大學的橋本昌宜教授等人組成的研究團隊,利用新奈米器件——通孔開關(Via-Switch)實現FPGA的程式設計功能,全球首次成功實現了FPGA晶片的12倍高密度安裝(圖a)。通過開發適合AI應用的FPGA架構,有望將能效提高5倍,同時通過採用半導體微細工藝,有望持續提高性能。

圖:利用新開發的通孔開關FPGA提高安裝密度的示意圖及布線截面圖

FPGA憑藉能在短時間内實現功能以及適合少量多品種產品的特性得到了廣泛利用。不過,要想實現晶片内的程式設計功能,仍需要使用大量電晶體。因此在晶片應用方面仍面臨安裝密度低、工作速度和耗電能等性能也較低的挑戰。

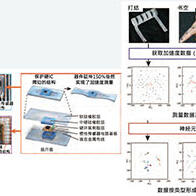

橋本教授的研究團隊一直在開發名為通孔開關的新型非易失開關器件。此次,全球首次成功試製了採用通孔開關的FPGA。經驗證,與利用電晶體實現程式設計功能的常規FPGA相比,安裝密度提高了12倍(圖a)。安裝密度直接關係到FPGA晶片的價格,此舉有望大幅降低成本。由於無需再利用電晶體實現程式設計功能,所有電晶體都可用於計算,因此還有望實現高計算性能。研究團隊對利用最小線寬為65nm的硅CMOS工藝製造的FPGA晶片進行了程式設計,確認能實現預期的功能。綜上,通孔開關是適合新一代FPGA的器件。

此外,研究團隊還開發了有效實現AI應用的FPGA架構,並進行了性能預測。預測發現,與利用電晶體實現程式設計功能的FPGA相比,能效可提高5倍。利用最小線寬為7nm的硅CMOS工藝製造時,能效還可再提高11倍。

該技術的詳細内容已在2月19日於美國舊金山舉行的最大規模半導體技術相關會議「國際固態電路會議ISSC 2020(IEEE International Solid-State Circuits Conference 2020)」上發表(發表序號33.3)。

論文資訊

題目:Via-Switch FPGA:65nm CMOS Implementation and Architecture Extension for AI Applications

發表編號:33.3

中文:JST客觀日本編輯部編譯整理