本文根據產綜研成果發布編譯整理而成

以日本國立研究開發法人產業技術綜合研究所(以下簡稱「產綜研」)器件技術研究部門尖端CMOS技術研究團隊的張文馨研究員為代表的日本團隊(產綜研和東北大學),與以國家實驗研究院臺灣半導體研究中心的李耀仁研究員為代表的臺灣團隊(國立交通大學、國立成功大學、國立暨南國際大學、國立臺灣大學、國立中山大學、逢甲大學、工業技術研究院、日立先端科技臺灣公司)經過聯合研究,面向2nm工藝開發出了Si和Ge的異質溝道互補式場效電晶體hCFET(heterogeneous Complementary-Field Effect Transistor)。

相關技術詳情將在2020年12月12~16日線上舉行的2020 IEEE International Electron Devices Meeting(IEDM 2020)上發表。

研究團隊此次開發了上下層疊Si和Ge的溝道薄膜的技術,實現了以最短距離連接Si n型FET和Ge p型FET的hCFET構造。通過縮小積體電路的三維結構,有望大幅提高整合度及進一步提高速度。

Si/Ge異質溝道互補式場效電晶體hCFET

開發背景

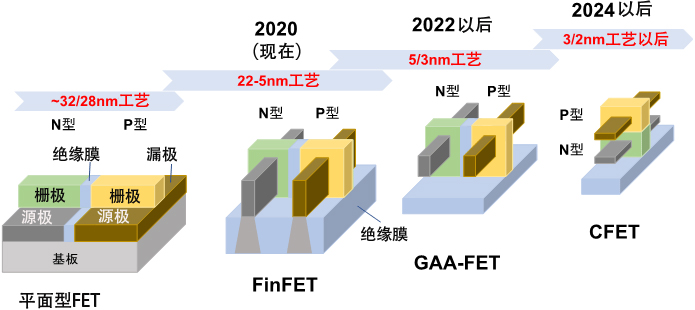

隨著移動資訊終端和IT設備等的放大性普及,電子資訊設備需要提高性能和削減耗電能。圖1是負責資訊處理的場效電晶體(FET)發展藍圖。通過推進FET的微細化,平面型CMOS結構遵循摩爾定律實現了高性能和低功耗,但二維結構的微細化達到了物理可用能極限,從22nm工藝前後開發端生重大變化,轉向了三維FET結構。Fin FET是擁有鰭(Fin)狀柵極結構的FET,目前已實用化。由其發展而來的是柵極完全覆蓋了溝道的上下左右部位的GAA(Gate All Around)結構。今後進一步演化的FET結構將是上下層疊n型FET和p型FET的CFET結構。這種結構能以原來的單個FET元件的尺寸構成CMOS,可以大幅削減面積和提高速度。

另一方面,Si以外的溝道材料的研究開發也在進行中。與Si相比,Ge的電洞遷移率比較高,能以低電壓工作,與Si工藝的親和性也比較高,因此n型FET利用原來的Si、p型FET利用Ge製作的異質溝道整合平台作為FET的高速化技術備受期待。

圖1:FET發展藍圖

研究内容

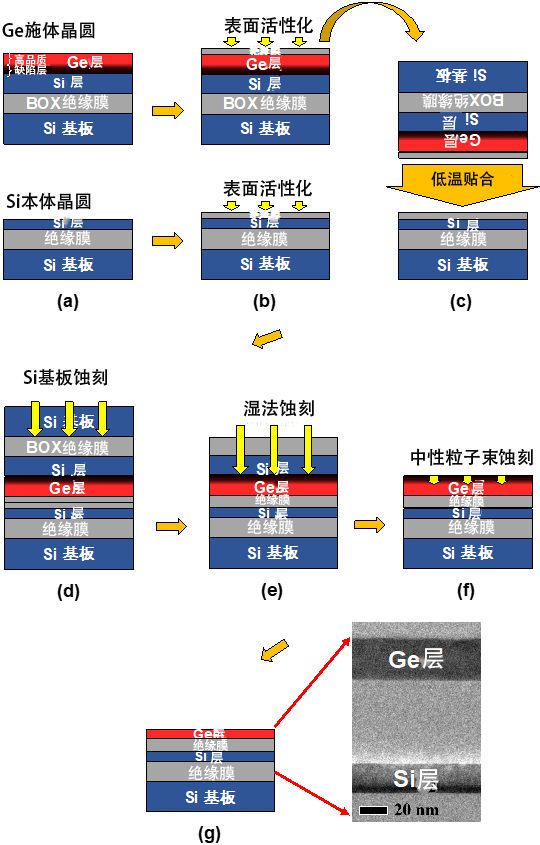

產綜研和TSRI構築了層疊Si層和Ge層的Si/Ge異質溝道整合平台。層疊Si和Ge等熱膨脹率不同的材料時,為避免熱應力的影響,需要在儘量低的溫度下進行層疊。研究團隊開發出了在低於200℃的溫度下層疊高品質Si層和Ge層的低溫異質層黏合技術(Low Temperature Hetero-layer Bonding Technology, LT-HBT,圖2)。

圖2:採用低溫異質層黏合技術的Si/Ge異質溝道積層工藝

此次開發的技術首先準備了SOI主體晶圓(Host Wafer)和在上面磊晶生長Ge的施體晶圓(Donor Wafer,a)。在Ge層中,與Si層的界面附近的位置存在缺陷層,表面側存在高品質層。接下來,分別在施體晶圓和主體晶圓上沉積物SiO2絕緣膜,激活表面後(b),以200度的低溫直接鍵合(c)。然後依次去除施體晶圓的Si基底層(d)、BOX絕緣膜和Si層(e)。最後,利用東北大學開發的可低傷害加工的中性粒子束蝕刻法(Neutral Beam Etching, NBE)將Ge均勻成膜(f),即可獲得Si/Ge異質溝道積層結構(g)。通過使積層工藝和蝕刻工藝全部在低溫下進行,實現了對Si層和Ge層的傷害非常小的高品質Si/Ge異質溝道整合平台。另外,利用該技術,不僅可以大幅簡化hCFET製作工藝,還支持進一步增加層數的結構。

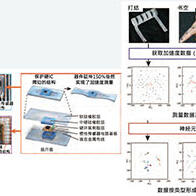

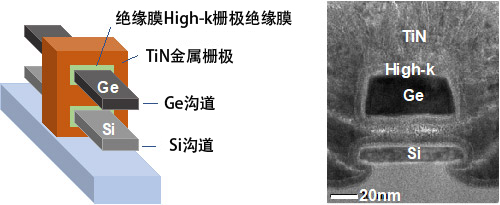

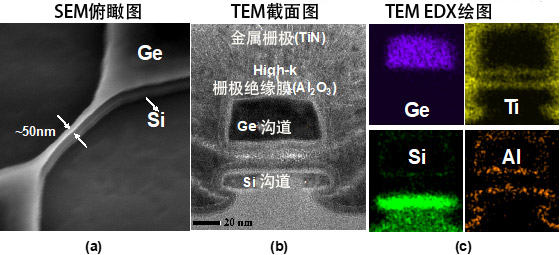

研究團隊利用該Si/Ge異質溝道積層平台製作了hCFET(圖3)。通過以相同的溝道圖案形成Si和Ge層,並對Si層與Ge層之間的絕緣進行蝕刻,得到了奈米片狀積層型溝道結構。從圖3(a)的SEM俯瞰圖可以看出,Ge和Si溝道是裸露的。通過以覆蓋整個溝道的形式在該結構上沉積物high-k柵極絕緣膜/金屬柵極,實現了上下層疊Si n型FET和Ge p型FET的GAA結構hCFET(圖3(b))。可以看到以溝道寬度約為50nm的奈米片狀在上部層疊Ge層,下部層疊Si層的結構。TEM EDX分析顯示,Si/Ge異質材料溝道被high-k柵極絕緣膜(Al2O3)和金屬柵極(TiN)覆蓋(圖3(c))。另外,還通過單一的柵極成功地使這些n型FET和p型FET同時作為電晶體工作,表明基於LT-HBT的異質溝道積層化作為2nm工藝的電晶體技術非常有效。

圖3:上下層疊Si n型FET和Ge p型FET的三維異質溝道互補式場效電晶體(hCFET)

日語發布資料

編譯:JST客觀日本編輯部