日本電信電話術公司(NTT)、九州大學、東京大學針對量子計算機的運轉進行動態糾錯,在全球首次提出了可大幅削減被視為故障容許度量子計算機發展障礙的突發錯誤影響的量子計算機架構。

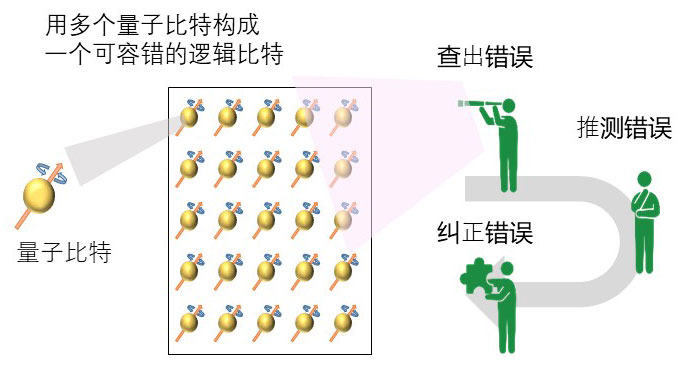

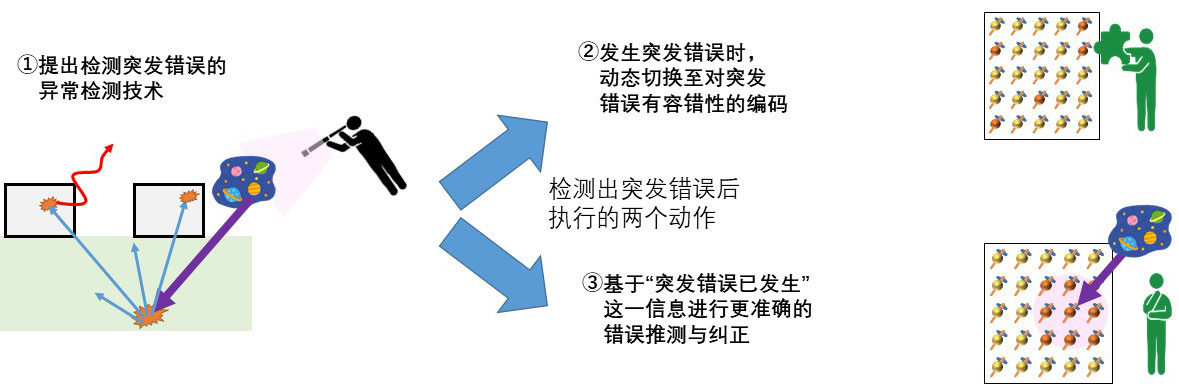

圖1糾錯示意圖(圖片由NTT提供)

量子位元只要持有的資訊洩漏到外部就會出錯,所以即便是不會導致普通計算機發生錯誤的環境噪聲,對量子計算機來說也會成為導致產生錯誤的原因。

近年來,隨著量子技術的發展,可控的量子位元數出現了增加,但隨著整合化的發展,計算中的低機率錯誤特性的變化會對量子糾錯的性能產生較大的影響。為此,還必須應對因宇宙射線產生的突發錯誤。

研究團隊提出的架構,能夠通過在控制量子計算機的普通計算機控制機構中追加邏輯單元,從而大幅降低超導量子位元因宇宙射線產生的突發錯誤的持續時間和影響範圍。這種方法無論在何種部件上,適用於滿足一定特性的任何突發錯誤。

該架構的關鍵在於異常檢測、動態編碼方式的變形和錯誤推測的再執行。首先是通過異常檢測技術,在短暫的延遲内檢測出突發錯誤的發生。研究團隊提出了一種檢測技術,此時並不直接測量量子位元,而是從被用作錯誤推測提示的奇偶校驗值的統計結果推測出突發錯誤的發生。

一旦通過異常檢測發現突發錯誤的發生,就會執行兩個用於減輕突發錯誤影響的動作。一是立即切換至效率雖低但對突發錯誤具有故障容許度性的編碼方式,此舉能夠在突發錯誤被檢測出後將其影響幾乎降至為零。這是一種以非嚴格對應進行中斷處理的編碼機制。與此同時,倒退回突發錯誤到來之前的狀態,基於「突發錯誤已發生」這一資訊進行更準確的錯誤推測,從而進一步減輕從突發錯誤的發生到被檢測出來這段時間裏產生的影響。

圖2)提出的方法:突發錯誤的檢測和應對(圖片由NTT提供)

研究表明即使將這樣的追加機制組裝到控制裝置中,也不會影響量子計算機本身的速度。

東京大學研究生院工學系研究科的小蘆雅鬥教授表示:「這可以說是實現大規模故障容許度量子計算機的一個重要進展。」

原文:《科學新聞》

翻譯:JST客觀日本編輯部

【論文資訊】

學會:在The 55th IEEE/ACM International Symposium on Microarchitecture(MICRO-55)

論文:Q3DE: A fault-tolerant quantum computer architecture for multi-bit burst errors by cosmic rays